# Micro SD Data Sheet

| Table of Contents                               |    |

|-------------------------------------------------|----|

| 1. Introduction to the micro SDSC/SDHC/SDXC     | 4  |

| 2. Micro SDSC/SDHC/SDXC Feature                 | 4  |

| 3. Product Specification                        | 6  |

| 4. Micro S SDSC/SDHC/SDXC Interface Description | 7  |

| 5. Mechanical Form Factor                       | 15 |

## **Revision History**

| Date     | Revision | History      |

|----------|----------|--------------|

| APR 2012 | 1.0      | New Creation |

## 1. Introduction to the micro SDSC/SDHC/SDXC

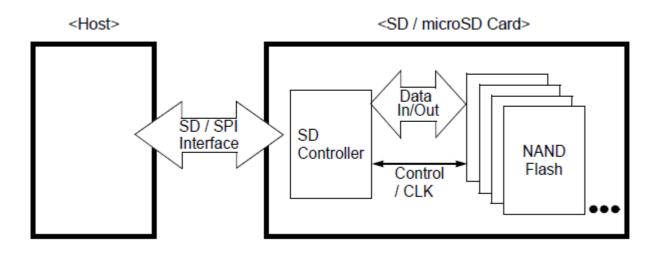

Micro SD Card is a Flash – Based memory card that is designed to meet the security, capacity, performance and environment requirements inherent to use in emerging audio and video electronic device.

The Micro SD Card communication is based on an advance 8-pin interface (clock, command, 4x Data and 2x power lines) and the Micro SD Memory Card host interface supports regular Multi Media Card operation as well.

## 2. System Features

%Targeted for portable and stationary applications

- \*Capacity of Memory

- (1) Standard Capacity SD Memory card (SDSC): Up to and including 2 GB

- (2) High Capacity SD Memory Card (SDHC): More than 2GB and up to and including 32GB

- (3) Extended Capacity SD Memory Card (SDXC): More than 32GB and up to and including 2TB

- % Voltage range:

- High Voltage SD Memory Card Operating voltage range: 2.7-3.6 V

- % Designed for read-only and read/write cards.

\*Compliant SD Card Specification ver. 3.01

- % Bus Speed Mode (using 4 parallel data lines)

- (1) Default Speed mode: 3.3V signaling, Frequency up to 25 MHz, up to 12.5 MB/sec

- (2) High Speed mode: 3.3V signaling, Frequency up to 50 MHz, up to 25 MB/sec

- (3) SDR12: 1.8V signaling, Frequency up to 25 MHz, up to 12.5MB/sec

- (4) SDR25: 1.8V signaling, Frequency up to 50 MHz, up to 25MB/sec

- (5) SDR50: 1.8V signaling, Frequency up to 100 MHz, up to 50MB/sec

- (6) SDR104: 1.8V signaling, Frequency up to 208 MHz, up to 104MB/sec

- (7) DDR50: 1.8V signaling, Frequency up to 50 MHz, sampled on both clock edges, up to 50MB/sec

- % Switch function command supports High-Speed, and future functions

- % Correction of memory field errors

- % Card removal during read operation will never harm the content

- % Content Protection Mechanism Complies with highest security of SDMI standard.

- %Password Protection of cards (CMD42 LOCK\_UNLOCK)

- % Write Protect feature using mechanical switch

- % Built-in write protection features (permanent and temporary)

- % Card Detection (Insertion/Removal)

- ※ Application specific commands

- %Comfortable erase mechanism

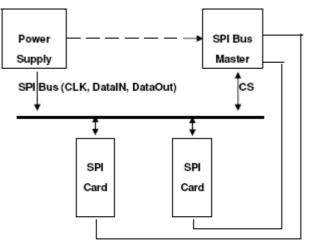

## 2.1 System Block Diagram

## 2.2 Speed Class

- % Five Speed Classes are defined and indicate minimum performance of the cards

- Class 0 These class cards do not specify performance. It includes all the legacy cards prior to

this specification, regardless of its performance

- Class 2 is more than or equal to 2 MB/sec performance

- Class 4 is more than or equal to 4 MB/sec performance

- ◆ Class 6 is more than or equal to 6 MB/sec performance

- Class 10 is more than or equal to 10 MB/sec performance

- % Dimension: 15.0mm x 11.0mm

- % Support CPRM

- % No external programming voltage required

- SD Memory Card protocol compatible

- % Targeted for portable and stationary applications for secured (copyrights protected) and non-secured data storage

- \* Correction of memory field errors

- % Copyrights Protection Mechanism: Complies with highest security of SDMI standard

- % Card Detection (Insertion / Removal)

- \* CE and FCC certificates

- % Easy handling for the end user

#### Notes: The performance depends on different test platform with different result.

· The communication channel is described in the table below

#### • Micro SDSC/SDHC/SDXC Bus/SPI Bus comparison

| Micro SDSC/SDHC/SDXC Using SD Bus               | Micro SDSC/SDHC/SDXC Using SPI Bus                         |

|-------------------------------------------------|------------------------------------------------------------|

| Six-wire communication channel                  | Three-wire serial data bus (Clock, dataIn, data Out )+card |

| (clock, command, 4 data lines)                  | specific CS signal(hardwired card selection)               |

| Error-protected data transfer                   | Optional non protected data transfer mode available        |

| Single or multiple block oriented data transfer | Single or multiple block oriented data transfer            |

## 3. Product Specification

## 3.1 Reliability and Durability Specifications

| Temperature                      | Operating: -25℃ to 85℃<br>Storage: -40℃(168h) to 85℃(500h)                                                                                        |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| moisture and corrosion           | Operating: 25 ℃ / 95% rel. humidity<br>Non-Operating: 40 ℃ / 93% rel. hum./500h<br>salt water spray:<br>3% NaCl/35C; 24h acc. MIL STD Method 1009 |

| Durability                       | 10,000 mating cycles                                                                                                                              |

| Bending                          | 10N                                                                                                                                               |

| Torque                           | 0.10N*m. ±2.5° max                                                                                                                                |

| Drop Test                        | 1.5m free fall                                                                                                                                    |

| Visual Inspection/Shape and Form | No warp age; no mold slim; complete form; no cavities; surface smoothness≦-0.1mm/ cm2 within contour; no cracks; no pollution (oil, dust, etc.)   |

## 3.2 System Reliability and Maintenance

| MTBF                   | >1,000,000 hours                            |

|------------------------|---------------------------------------------|

| Preventive Maintenance | None                                        |

| Data Reliability       | < 1 non-recoverable error in 1014 bits read |

| Endurance              | MLC 3,000~10,000 write/erase cycles         |

|                        | TLC 500~1,000 write/erase cycles            |

## 3.3 Electrical Static Discharge (ESD) requirement

| ESD Protection | Contact Discharge: | ±4KV, Human body model according to<br>IEC61000-4-2.EN55024 |

|----------------|--------------------|-------------------------------------------------------------|

|                | Air Discharge;     | ±8KV, Human body model according to IEC61000-4-2.EN55024    |

## 4. Micro SDSC/SDHC/SCXC Interface Description

#### 4.1 General Description of Pins and Registers

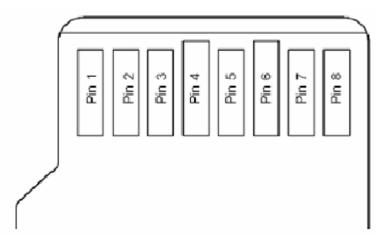

The Micro SDHC has nine exposed contacts on one side. The host is connected to the SD Memory Card using a eight pin connector.

#### Pin Assignment in SD Bus Mode Pad Definition

| Pin # | Name    | Туре | Micro SD Description          |  |  |

|-------|---------|------|-------------------------------|--|--|

| 1     | DAT2    | I/O  | Card Detect/ Data Lin [Bit 3] |  |  |

| 2     | CD/DAT3 | I/O  | Card Detect / Data Line       |  |  |

| 3     | CMD     | PP   | Command / Response            |  |  |

| 4     | VDD     | S    | Supply voltage                |  |  |

| 5     | CLK     | I    | Clock                         |  |  |

| 6     | Vss     | S    | Supply voltage ground         |  |  |

| 7     | DAT0    | I/O  | Data Line [Bit 0]             |  |  |

| 8     | DAT1    | I/O  | Data Line [Bit 1]             |  |  |

Note:

1) S=power supply; l=input; O=output using push-pull drivers.

2) The extended DAT lines (DAT1-DAT3) are input on power up; they start to operate as DAT lines after the SET \_BUS\_WIDTH command.

3) After power up, this line is input with 50Kohm pull-up (can be used for card detection or SPI mode selection). The pull-up should be disconnected by the user, during regular data transfer, with SET\_CLR\_CARD\_DETECT (ACMD42) command.

#### Pin Assignment in SPI Bus Mode Pad Definition

| Pin # | Name | Туре | Micro SD Description   |  |  |

|-------|------|------|------------------------|--|--|

| 1     | RSV  |      | Reserved               |  |  |

| 2     | CS   | I    | Chip Select (neg true) |  |  |

| 3     | DI   | S    | Data In                |  |  |

| 4     | VDD  | S    | Supply Voltage         |  |  |

| 5     | SCLK |      | Clock                  |  |  |

| 6     | VSS  | S    | Supply Voltage Ground  |  |  |

| 7     | DO   | 0    | Data Out               |  |  |

| 8     | RSV  | I    | Reserved               |  |  |

#### Each card has a set of information registers

#### **Micro SD Memory Card Registers**

| Name | Width | Description                                                                                                                            |

|------|-------|----------------------------------------------------------------------------------------------------------------------------------------|

| CID  | 128   | Card identification number: individual card number for identification.                                                                 |

| RCA  | 16    | Relative card address: local system address of a card dynamically suggested by the card and approved by the host during initialization |

| CSD  | 128   | Card specific data: information about the card operation conditions.                                                                   |

| SCR  | 64    | SD Configuration Register: information about the Micro SD Card's special feature capabilities.                                         |

| OCR  | 32    | Operation Condition Register                                                                                                           |

The host may reset the cards by switching the power supply off and on again. The card has its own power-on detection circuitry which puts the card into an idle state after the power-on. The card can also be reset by sending the GO\_IDLE (CMD0) command.

## Micro SD memory Card Pin Assignment

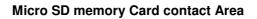

#### 4.2 SD Bus Topology

The SD bus has six communication lines and three supply lines:

- CMD: Command is bi-directional signal.(Host and card drivers are operating in push pull mode.)

- DAT0-3: Data lines are bi-directional signals. (Host and card drivers are operating in push pull mode.).

- · CLK: Clock is a host to cards signal. (CLK operates in push pull mode.)

- VDD: VDD is the power supply line for all cards.

- VSS [1:2]: VSS are two ground lines.

- The following figure shows the bus topology of several cards with one host in SD Bus mode.

Micro SD Memory Card System Bus Topology

During the initialization process, commands are sent to each card individually, allowing the application to detect the cards and assign logical addresses to the physical slots. Data is always sent to each card individually. However, to simplify the handling of the card stack, after initialization, all commands may be sent concurrently to all cards. Addressing information is provided in the command packet.

The Micro SD Bus allows dynamic configuration of the number of data lines. After power-up, by default, the Micro SD Memory Card will use only DAT0 for data transfer. After initialization, the host can change the bus width (number of active data lines). This feature allows and easy trade off between hardware cost and system performance.

#### 4.2.1 Power Protection

Card can be inserted into or removed from the bus without damage. If one of the supply pins (VDD or Vss ) is not connected properly, then the current is drawn through a data line to supply the card.

Data transfer operations are protected by CRC codes; therefore, any bit changes induced by card insertion and removal can be detected by the Micro SD bus master. The inserted card must be properly reset also when CLK carries a clock frequency fpp.

If the hot insertion feature is implemented in the host, than the host has to withstand a shortcut between VDD and Vss without damage.

#### 4.3 SPI Bus Topology

The memory Card SPI interface is compatible with SPI hosts available on the market. As any other SPI device the Micro SD Memory Card SPI channel consists of the following 4 signals:

1) CS: Host to card Chip Select signal.

2) SCLK: Host to card clock signal.

3) Data In: Host to card data signal.

4) Data Out: Card to host data signal.

Another SPI common characteristic, which is implemented in the Memory Card as well, is byte transfers. All data tokens are multiples of 8 bit bytes and always byte aligned to the CS signal.

The SPI standard defines the physical link only and not the complete data transfer protocol. In SPI Bus mode, the Micro SD Memory Card uses a subset of the Micro SD Memory Card protocol and command set.

The Micro SD Memory Card identification and addressing algorithms are replaced by a hardware Chip Select (CS) signal.

A card (slave) is selected, for every command, by asserting (active low) the CS signal.

The CS signal must be continuously active for the duration of the SPI transaction (command, response and data). The only exception is card programming time. At this time the host can de-assert the CS signal without affecting the programming process.

The bi-directional CMD and DAT lines are replaced by uni-directional data In and data Out signals. This eliminates the ability of executing commands while data is being read or written. An exception is the multi read/write operations. The Stop Transmission command can be sent during data read. In the multi block write operation a Stop Transmission token is sent as the first byte of the data block.

SD Memory Card Bus System

#### 4.4 Electrical Interface

The power up of the SD Memory Card bus is handled locally in each SD Memory Card and in the bus master.

#### 4.4.1 Operating Conditions

SPI Mode bus operating conditions are identical to SD Memory Card mode bus operating conditions. The CS (chip select) signal timing is identical to the input signal timing.

#### Power Supply Voltage

| General                                   |                                 |           |       |      |        |  |  |

|-------------------------------------------|---------------------------------|-----------|-------|------|--------|--|--|

| Parameter                                 | Symbol                          | Min.      | Max.  | Unit | Remark |  |  |

| Peak voltage on all lines                 |                                 | -0.3      | 3.6   | v    |        |  |  |

|                                           | All Inputs                      |           |       |      |        |  |  |

| Input Leakage Current                     | Input Leakage Current -10 10 uA |           |       |      |        |  |  |

|                                           | All Outputs                     |           |       |      |        |  |  |

| Output Leakage Current                    |                                 | -10       | 10    | uA   |        |  |  |

|                                           | Power                           | supply Vo | Itage |      |        |  |  |

| Parameter                                 | Symbol                          | Min.      | Max.  | Unit | Remark |  |  |

| Supply Voltage for High voltage range     | VDDH                            | 2.7       | 3.6   | v    |        |  |  |

| Supply voltage differentials (Vss1, Vss2) |                                 | -0.5      | 0.5   | v    |        |  |  |

#### **Bus Signal Line Load**

The total capacitance CL of the CLK line of the SD Memory Card bus is the sum of the bus master capacitance CHOST, the bus capacitance CBUS itself and the capacitance CCARD of each card connected to this line:

#### CL = CHOST + CBUS + N \* CCARD

Where N is the number of connected cards. Requiring the sum of the host and bus capacitances not to exceed 30 pF for up to 10 cards, and 40 pF for up to 30 cards, the following values must not be exceeded:

Signal Line's Load

| Parameter                                  | Symbol | Min. | Max. | Unit | Remark                                               |

|--------------------------------------------|--------|------|------|------|------------------------------------------------------|

| Pull-up resistance                         | RCMD   | 10   | 100  | kΩ   | To prevent bus floating                              |

| Total Bus capacitance for each signal line | сL     |      | 40   | pF   | Single Card CHOST<br>+CBUS Shall not exceed<br>30 pF |

| Maximum signal line inductance             |        |      | 16   | nH   | fPP ≤20 MHz                                          |

| Pull-up resistance inside card (pin1)      | RDATS  | 10   | 90   | kΩ   | May be used for card<br>detection                    |

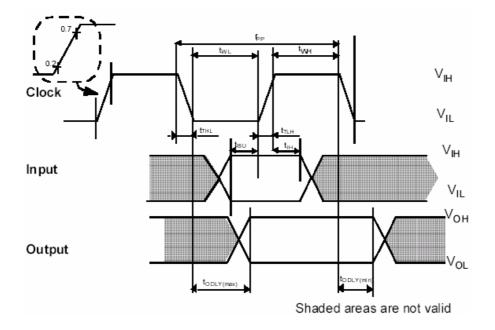

### 4.4.2 Bus Timing (Default)

#### Timing Diagram Data Input. Output Referenced to Clock

#### Bus Timing (default mode)

| Parameter                                                      | Symbol     | Min.       | Max.    | Unit | Remark |  |  |  |

|----------------------------------------------------------------|------------|------------|---------|------|--------|--|--|--|

| Clock CLK (All values are referred to min.(VIH) and max.(VIL)) |            |            |         |      |        |  |  |  |

| Clock Frequency Data Transfer Mode                             | fPP        | 0          | 25      | MHz  |        |  |  |  |

| Clock Frequency Identification Mode(The                        |            |            |         |      |        |  |  |  |

| low frequency is required for SDCard                           | fop        | 0          | 400     | KHz  |        |  |  |  |

| compatibility)                                                 |            |            |         |      |        |  |  |  |

| Clock Low Time                                                 | tWL        | 10         |         | ns   |        |  |  |  |

| Clock High Time                                                | twн        | 10         |         | ns   |        |  |  |  |

| Inputs CM                                                      | ND,DAT(ref | erenced to | CLK)    |      |        |  |  |  |

| Input set-up time                                              | tisu       | 5          |         | ns   |        |  |  |  |

| Input hold time                                                | tін        | 5          |         | ns   |        |  |  |  |

| Outputs C                                                      | MD, DAT(re | ferenced   | to CLK) |      |        |  |  |  |

| Output delay time during Data Transfer                         | 100111     |            | 14      |      |        |  |  |  |

| Mode                                                           | tODLY      |            | 14      | ns   |        |  |  |  |

| Output delay time during Identification                        | topuy      |            | 50      | ns   |        |  |  |  |

| Mode                                                           | tODLY      |            | - 30    | 115  |        |  |  |  |

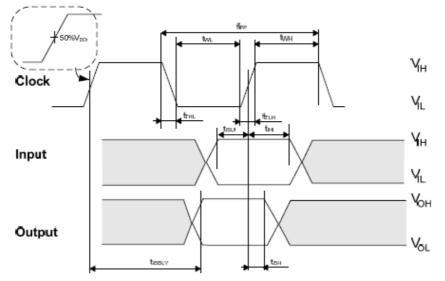

#### 4.4.3 Bus Timing (High-Speed Mode)

Shaded areas are not valid

| Parameter                                     | Symbol                                  | Min | Max. | Unit | Remark                                |

|-----------------------------------------------|-----------------------------------------|-----|------|------|---------------------------------------|

| Clock CLK (All values are referred to min (VI | <sub>H</sub> ) and max (V <sub>IL</sub> | ),  |      |      | •                                     |

| Clock frequency Data Transfer Mode            | f <sub>PP</sub>                         | 0   | 50   | MHz  | C <sub>CARD</sub> ≤ 10 pF<br>(1 card) |

| Clock low time                                | t <sub>WL</sub>                         | 7   |      | ns   | C <sub>CARD</sub> ≤ 10 pF<br>(1 card) |

| Clock high time                               | t <sub>WH</sub>                         | 7   |      | ns   | C <sub>CARD</sub> ≤ 10 pF<br>(1 card) |

| Clock rise time                               | t <sub>TLH</sub>                        |     | 3    | ns   | C <sub>CARD</sub> ≤ 10 pF<br>(1 card) |

| Clock fall time                               | t <sub>THL</sub>                        |     | 3    | ns   | C <sub>CARD</sub> ≤ 10 pF<br>(1 card) |

| Inputs CMD, DAT (referenced to CLK)           |                                         |     |      |      |                                       |

| Input set-up time                             | t <sub>ISU</sub>                        | 6   |      | ns   | C <sub>CARD</sub> ≤ 10 pF<br>(1 card) |

| Input hold time                               | t <sub>IH</sub>                         | 2   |      | ns   | C <sub>CARD</sub> ≤ 10 pF             |

| Parameter                                           | Symbol            | Min | Max. | Unit | Remark                             |

|-----------------------------------------------------|-------------------|-----|------|------|------------------------------------|

|                                                     |                   |     |      |      | (1 card)                           |

| Outputs CMD, DAT (referenced to CLK)                |                   |     |      |      |                                    |

| Output Delay time during Data Transfer Mode         | t <sub>ODLY</sub> |     | 14   | ns   | C <sub>L</sub> ≤ 40 pF<br>(1 card) |

| Output Hold time                                    | t <sub>OH</sub>   | 2.5 |      | ns   | C <sub>L</sub> ≥ 15pF<br>(1 card)  |

| Total System capacitance for each line <sup>1</sup> | CL                |     | 40   | pF   | 1 card                             |

1) In order to satisfy severe timing, host shall drive only one card.

#### 4.5 Micro SDSC/SDHC /SDXC Registers

There is a set of seven registers within the card interface. The OCR, CID, CSD and SCR registers carry the card configuration information. The RCA register holds the card relative communication address for the current session. The card status and SD status registers hold the communication protocol related status of the card.

#### 4.5.1 Operating Conditions Register (OCR)

The 32-bit operation conditions register stores the VDD voltage profile of the card. The SD Memory Card is capable of executing the voltage recognition procedure (CMD1) with any standard SD Memory Card host using operating voltages form 2 to 3.6 Volts.

Accessing the data in the memory array, however, requires 2.7 to 3.6 Volts. The OCR shows the voltage range in which the card data can be accessed. The structure of the OCR register is described in under table.

| OCR Bit | VDD Voltage Window              |  |  |  |  |

|---------|---------------------------------|--|--|--|--|

| 0-3     | Reserved                        |  |  |  |  |

| 4       | Reserved                        |  |  |  |  |

| 5       | Reserved                        |  |  |  |  |

| 6       | Reserved                        |  |  |  |  |

| 7       | Reserved                        |  |  |  |  |

| 8       | Reserved                        |  |  |  |  |

| 9       | Reserved                        |  |  |  |  |

| 10      | Reserved                        |  |  |  |  |

| 11      | Reserved                        |  |  |  |  |

| 12      | Reserved                        |  |  |  |  |

| 13      | Reserved                        |  |  |  |  |

| 14      | Reserved                        |  |  |  |  |

| 15      | 2.7-2.8                         |  |  |  |  |

| 16      | 2.8-2.9                         |  |  |  |  |

| 17      | 2.9-3.0                         |  |  |  |  |

| 18      | 3.0-3.1                         |  |  |  |  |

| 19      | 3.1-3.2                         |  |  |  |  |

| 20      | 3.2-3.3                         |  |  |  |  |

| 21      | 3.3-3.4                         |  |  |  |  |

| 22      | 3.4-3.5                         |  |  |  |  |

| 23      | 3.5-3.6                         |  |  |  |  |

| 24-29   | Reserved                        |  |  |  |  |

| 30      | Card Capacity Status (CCS)      |  |  |  |  |

| 31      | Card power up status bit (busy) |  |  |  |  |

#### OCR Register Definition

#### 4.5.2 Card Identification (CID) Register

The CID register is 16 bytes long and contains a unique card identification number as shown in the table below. It is programmed during card manufacturing and can not be changed by SD Memory Card hosts. Note that the CID register in the SD Memory Card has a different structure than the CID register in the Multimedia Card

| Name                         | Type   | Width | CID - Slice | Comments                                                                               |

|------------------------------|--------|-------|-------------|----------------------------------------------------------------------------------------|

| Manufacturer ID(MID)         | Binary | 8     | [127:120]   | The manufacturer IDs are controlled and assigned<br>by the SD Memory Card Association. |

| OEM/Application ID(OID)      | ASC∏   | 16    | [119:104]   | Identifies the card OEM and/or the card contents.<br>The OID is assigned by the 3C.    |

| Product Name(PNM)            | ASC II | 40    | [103:64]    | 5ASC  characters long                                                                  |

| Product Revision (PRV)       | BCD    | 8     | [63:56]     | Two binary coded decimal digits                                                        |

| Serial Number (PSN)          | Binary | 32    | [55:24]     | 32 Bits unsigned integer                                                               |

| Reserved                     |        | 4     | [23:20]     |                                                                                        |

| Manufacturing Data Code(MDT) | BCD    | 12    | [19:8]      | Manufacturing date-yym(offset from 2000)                                               |

| CRC7 checksum(CRC)           | Binary | 7     | [7:1]       | Calculated                                                                             |

| Not used, always '1'         |        | 1     | [0:0]       |                                                                                        |

#### CID Fields

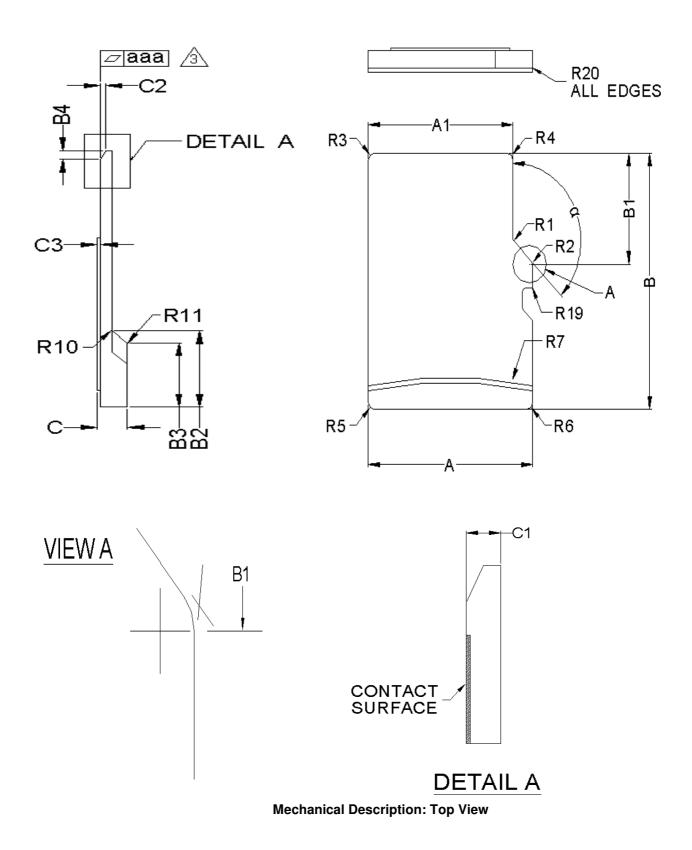

## 5. Mechanical Form Factor

| COMMON DIMENSIONS |          |       |       |          |  |  |

|-------------------|----------|-------|-------|----------|--|--|

|                   |          | NOTE  |       |          |  |  |

| SYMBOL            | MIN      | NOM   | MAX   | NOTE     |  |  |

| A                 | 10.90    | 11.00 | 11.10 |          |  |  |

| <u>A1</u>         | 9.60     | 9.70  | 9.80  | D A GLG  |  |  |

| A2                | -        | 3.85  | -     | BASIC    |  |  |

| A3                | 7.60     | 7.70  | 7.80  | 5.4.67.6 |  |  |

| A4                | -        | 1.10  | -     | BASIC    |  |  |

| A5                | 0.75     | 0.80  | 0.85  |          |  |  |

| <u>A6</u>         | -        | -     | 8.50  |          |  |  |

| A7                | 0.90     | -     | -     |          |  |  |

| A8                | 0.60     | 0.70  | 0.80  |          |  |  |

| A9                | 0.80     | -     | -     |          |  |  |

| A10               | 1.35     | 1.40  | 1.45  |          |  |  |

| A11               | 6.50     | 6.60  | 6.70  |          |  |  |

| A12               | 0.50     | 0.55  | 0.60  |          |  |  |

| A13               | 0.40     | 0.45  | 0.50  |          |  |  |

| В                 | 14.90    | 15.00 | 15.10 |          |  |  |

| B1                | 6.30     | 6.40  | 6.50  |          |  |  |

| B2                | 1.64     | 1.84  | 2.04  |          |  |  |

| B3                | 1.30     | 1.50  | 1.70  |          |  |  |

| B4                | 0.42     | 0.52  | 0.62  |          |  |  |

| B5                | 2.80     | 2.90  | 3.00  |          |  |  |

| B6                | 5.50     | -     | -     |          |  |  |

| B7                | 0.20     | 0.30  | 0.40  |          |  |  |

| B8                | 1.00     | 1.10  | 1.20  |          |  |  |

| B9                | -        | -     | 9.00  |          |  |  |

| B10               | 7.80     | 7.90  | 8.00  |          |  |  |

| B11               | 1.10     | 1.20  | 1.30  |          |  |  |

| B12               | 3.60     | 3.70  | 3.80  |          |  |  |

| B12               | 2.80     | 2.90  | 3.00  |          |  |  |

| B14               | 8.20     | -     | -     |          |  |  |

| B15               | -        | _     | 6.20  |          |  |  |

| C                 | 0.90     | 1.00  | 1.10  |          |  |  |

| <u>C1</u>         | 0.60     | 0.70  | 0.80  |          |  |  |

| C2                | 0.00     | 0.30  | 0.40  |          |  |  |

| C3                | 0.00     | 0.50  | 0.15  |          |  |  |

| D1                | 1.00     | _     | 0.15  |          |  |  |

| D1<br>D2          | 1.00     | -     | _     |          |  |  |

| D2<br>D3          | 1.00     | _     | _     |          |  |  |

| R1                | 0.20     | 0.40  | 0.60  |          |  |  |

| R1<br>R2          | 0.20     | 0.40  | 0.60  |          |  |  |

| R2<br>R3          | 0.20     | 0.40  | 0.00  |          |  |  |

|                   |          |       |       |          |  |  |

| R4                | 0.70     | 0.80  | 0.90  |          |  |  |

| R5                | 0.60     | 0.80  | 0.90  |          |  |  |

| R6                | 0.60     | 0.80  | 0.90  |          |  |  |

| R7                | 29.50    | 30.00 | 30.50 |          |  |  |

| R10               | -        | 0.20  | -     |          |  |  |

| R11               | -        | 0.20  | -     |          |  |  |

| R17               | 0.10     | 0.20  | 0.30  |          |  |  |

| R18               | 0.20     | 0.40  | 0.60  |          |  |  |

| R19               | 0.05     | -     | 0.20  |          |  |  |

| R20               | <u>A</u> | -     | 0.15  |          |  |  |

| α                 | 133°     | 135°  | 137°  |          |  |  |

| aaa               |          |       | 0.10  |          |  |  |

## Micro SDSC / SDHC / SDXC

Notes :

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M 1994.

- 2. DIMENSIONS ARE IN MILLIMETERS.

- <u>A</u> COPLANARITY IS ADDITIVE TO C1 MAX THICKNESS.

- ALL EDGES SHALL NOT BE SHARP AS TESTED PER UL1439 "Test for Sharpness of Edges on Equipment."

- 5. Refer to Appendix E about test method of warpage.

**Micro SD Package : Dimensions**